摩尔定律的终结将使服务于特定领域的架构成为计算的未来。一个开创性的例子就是谷歌在 2015 年推出的张量处理单元(TPU),目前已经在为超过十亿人提供服务。TPU 使深度神经网络(DNN)的计算速度提高了 15-30 倍,能耗效率比类似技术下的当代 CPU 和 GPU 高出了 30-80 倍。

虽然 TPU 是一种专用集成电路,但它运行的程序来自 TensorFlow 框架下的神经网络,驱动了谷歌数据中心的许多重要应用,包括图像识别、翻译、搜索和游戏。

通过专门为神经网络重新分配芯片计算资源,TPU 在真实数据中心负载环境下效率要比通用类型的计算机高 30-80 倍,目前已为全球 10 亿人提供日常服务。

神经网络的推理阶段通常会有严格的响应时间要求,这降低了通用计算机所使用技术的有效性;通用计算机通常运行得较快,但某些情况下也会较慢。

核心观点

所有指数增长都将有结尾

1965 年,据英特尔创始人之一的 Gordon Moore 预测,芯片中的晶体管数量每一两年都会增加一倍。尽管 2017 年 1 月的 ACM 通讯封面呼吁道:“担心我会终结简直是杞人忧天”,摩尔定律确实还是寿终正寝了。2014 年推出的 DRAM 芯片包含了 80 亿个晶体管,而在人们的预测中即使到了 2019 年,带有 160 亿个晶体管的 DRAM 芯片也不会大规模生产,但根据摩尔定律的预测,四年里晶体管数量应该变成四倍多。2010 年款的英特尔至强 E5 处理器拥有 23 亿个晶体管,而 2016 年的至强 E5 也只有 72 亿个晶体管,或者说比摩尔定律预计的数值低 2.5 倍——显然,纵使半导体行业还在进步,但其脚步已十分缓慢。

Dennard Scaling 是一个鲜为人知,但同样重要的观察结果。Robert Dennard 在 1974 年认为,晶体管不断变小,但芯片的功率密度不变。如果晶体管尺寸线性缩小两倍,那么同样面积上芯片中晶体管的数量就会变为 4 倍。同时,如果电流和电压都降低了二分之一,它所使用的功率将下降 4 倍,在相同的频率下提供相同的功率。Dennard Scaling 在被发现的 30 年后结束,其原因并不是因为晶体管的尺寸不再缩小,而是因为电流和电压不能在继续下降的同时保持可靠性了。

计算架构师们一直笃定摩尔定律和 Dennard Scaling,并通过复杂的处理器设计和内存层次结构,将资源转化为性能,这些设计利用了不同的处理指令的之间的并行性,但架构师们并没有什么编程的知识。ε=(´ο`*))) 唉,于是架构师们最终还是再也找不到新的办法可以利用指令级别的并行性。Dennard Scaling在 2004 年终结了,祸不单行的是继续提升指令级别并行性的方法也开始缺席,这迫使业界只能从单核高耗能处理器转换到多核高效率处理器。

今天我们仍然遵守吉恩·阿姆达尔(IBM 着名工程师,阿姆达尔定律的提出者)在 1967 年提出的定律,该定律认为不断增加处理器数量会导致性能提升的递减。阿姆达尔定律说,并行计算的理论加速受到任务顺序部分的限制;如果任务的 1/8 是串行的,则最大加速也只比原始性能高 8 倍——即使任务的其余部分很容易并行,并且架构师增加了 100 个处理器也是如此。

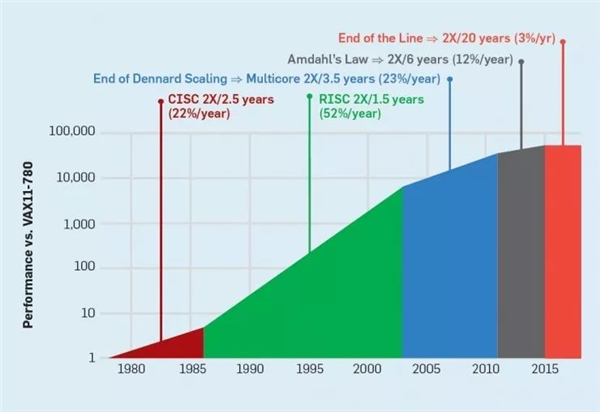

下图显示了过去四十年以来,上述三大定律对处理器性能的影响。按照目前的速度,标准处理器的性能在 2038 年以前都不会再次翻倍。

图 1. 依照Hennessy和Patterson的理论,我们绘制了过去40年中,32位和64位处理器内核每年最高的SPECCPUint性能;面向吞吐量的SPECCPUint_rate反映了类似的情况,即使其平稳期延迟了几年

晶体管看来没什么进步空间了(这反映了摩尔定律的结束),而每平方毫米芯片面积的功耗正在增加(毕竟 Dennard Scaling 也结束了),但人们对于芯片的功率预算却并没有增加(因为电子的移动、机械和发热限制),芯片设计师们已经在充分发挥多核心的能力了(但这也受到阿姆达尔定律的限制),架构师们现在普遍认为,能显着改进性能、价格、能源三者平衡的唯一途径就是特定领域的架构——它们只适用于处理几种特定的任务,但效率非常高。

在云端的大型数据集和大量计算机之间的协作使得机器学习近年来有了很大的进步,特别是在深度神经网络(DNN)方面。与一些其他领域不同,DNN 的应用方式很广泛。DNN 的突破性进展包括将语音识别的单词错误率相比老方法降低了 30%,这是近 20 年来最大的单次提升;自 2011 年以来,将图像识别的错误率从 26% 降低至 3.5%;在围棋上击败了人类世界冠军;改进了搜索排名等等。单个 DNN 架构或许应用范围很窄,但这种方法仍然催生出了大量实际应用。

神经网络类似于人脑中神经的功能,基于简单的人工神经元,它们是输入的加权和的非线性函数,例如 max(0,value)。这些人工神经元被分为许多不同的层,其中一层的输出就会作为下一层的输入。深度神经网络中的“深层”代表有多个层,由于云上有极大的数据集,只需换用更大、更多的层就可以构建出更准确的模型,它也就可以获取更高阶抽象的模式或是概念,而 GPU 可以提供足够的计算能力帮我们开发 DNN。

DNN 运行的两个阶段被称为训练(或学习)和推理(或预测),分别指代开发与生产。训练一个 DNN 可能需要数天,但训练好的 DNN 进行推理只需要几毫秒。针对不同的应用,开发者需要选择神经网络的类型和层数,而训练过程会决定网络中的权重。几乎所有的训练都是浮点运算,这就是 GPU 在深度学习时代如此受欢迎的原因之一。

被称为“量化”的转换将浮点型转为整型,整型通常只有 8 位——这种程度通常足以满足推理的要求了。与 IEEE 754 16 位浮点乘法相比,8 位整型乘法只需要 1/6 的能耗,需要的空间也只需要 1/6,而转换为整型加法也能带来 13 倍能耗和 38 倍空间的提升。

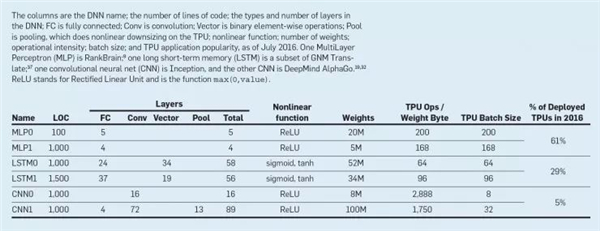

下表展示了两个例子,共三类、六个 DNN 实例的运行效率——这代表了谷歌数据中心 2016 年 95% 的深度神经网络推理工作负载,我们把它们作为 benchmark。它们在 TensorFlow 中的代码都非常短,只有 100-1500 行。这些例子是主服务器上运行较大应用程序中的小组件,这些大应用可能会由数千到数百万行 C++代码构成。应用程序通常面向用户,这就对响应时间带来了严格的要求。

表 1. 2016年7月,谷歌TPU上的DNN工作负载。共六种DNN应用(三种DNN类型),代表95%的TPU工作负载

如表 1 所示,每个模型需要 500 万至 1 亿个权重,即便只是访问这些权重都需要花费大量时间和能耗。为了降低访问成本,在训练或者推理中会针对一批完全不相干的输入样本都使用同样的权重,这种做法可以提高性能。

TPU 起源、架构及实现

早在 2006 年,谷歌就开始考虑在其数据中心部署 GPU(图形处理器),或者 FPGA (field programmable gate array,现场可编程门阵列),或者专用集成电路(ASIC)。当时的结论是,能在专门的硬件上运行的应用并不多,它们使用谷歌大型数据中心的富余计算能力即可,基本可以看做是免费的,另外也很难不怎么花钱就带来很大改进。情况在 2013 年出现了变化,当时谷歌用户每天使用语音识别 DNN 语音搜索三分钟,使得谷歌数据中心的计算需求增加了一倍,而如果使用传统的 CPU 将非常昂贵。因此,谷歌启动了一项优先级别非常高的项目,快速生产一款定制芯片用于推理,并购买现成的 GPU 用于训练。谷歌的目标是将性价比提高 10 倍。为了完成这项任务,谷歌在其数据中心设计、验证、构建并部署了 TPU,而这一过程仅仅用了 15 个月。

为了降低部署推迟的风险,谷歌工程师将 TPU 设计成 I/O 总线上的协处理器,并允许它像 GPU 一样插入现有服务器,而不是使 TPU 与 CPU 紧密集成。此外,为了简化硬件设计和调试,主机服务器将指令发送给 TPU 令其执行,而不是让 TPU 去自行获取。因此,TPU 在理念上更接近浮点单元(FPU)协处理器,而不是 GPU。

谷歌工程师将 TPU 看做一个系统进行优化。为了减少与主机 CPU 的交互,TPU 运行整个推理模型,但提供了与 2015 年及以后的 DNN 相匹配的灵活性,而不局限于 2013 年的 DNN。

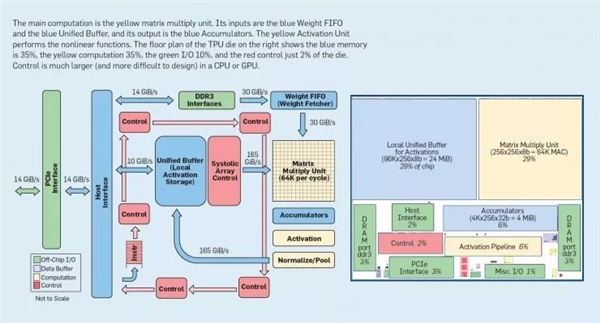

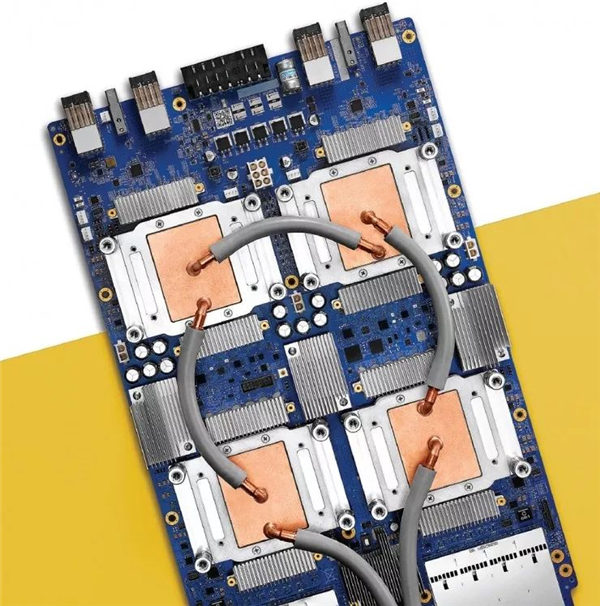

TPU 指令通过 PCI-e Gen3x16 总线从主机被发送到指令缓冲器中。内部计算模块通常通过 256 字节宽度的路径连接在一起。对于右侧的芯片布局图,从右上角开始,矩阵乘法单元是 TPU 的核心,256×256 MAC 可以对有符号或无符号的整型执行 8 位乘法和加法运算。得到的 16 位的结果会存入矩阵计算单元下方的共 4MB 空间的 32 位累加器中。这四个 MiB 代表含有 4,096 个 256 元素的 32 位累加器。矩阵计算单元每周期产生一个 256 元素的部分和。

图 2. TPU架构示意图及芯片布局图

矩阵单元的权重通过片内「权重 FIFO」来分级,该 FIFO 从我们称之为「权重存储器」的片外 8GB DRAM 中读取;对于推理,权重仅作读取;8GB 空间可以支持同时激活多个模型。权重 FIFO 有四层深。中间结果保存在 24MiB 的片上「统一缓冲器」中,可以作为矩阵计算单元的输入。可编程 DMA 控制器会z z哎CPU 主机存储器和统一缓冲器间传送数据。为了能在谷歌的规模上可靠地部署,内存储器和外存储器包含内置错误检查与纠正硬件。

TPU 微架构的原理是保持矩阵计算单元一直在工作中。为了实现这一目标,读取权重的指令遵循解耦访问/执行原理,它可以在发送权重的地址之后、但从权重存储器中取出权重之前完成一条指令。如果输入激活或权重数据没有准备好,矩阵计算单元将停止。

由于读取大型静态随机存取存储器(Static Random-Access Memory,SRAM)消耗的能源比数学运算多得多,矩阵单元使用「脉动执行」通过减少统一缓冲器的读写来节约能量。来自不同方向的数据以规律的间隔到达阵列中的单元,然后进行组合计算。一个含有 65,536 个元素的向量-矩阵乘法运算作为对角波前在矩阵中移动。这些权重被预加载,并随着新数据块的第一个数据一起随着前进波生效。控制和数据被流水线化,给程序员一种错觉,仿佛 256 个输入是一次读取的,并立即更新 256 个累加器中每个累加器的一个位置。从正确性的角度来看,软件不了解矩阵单元的脉动特性,但为了提高性能,必须考虑单元的延迟。

TPU 软件栈必须与为 CPU 和 GPU 开发的软件栈兼容,这样应用可以快速移植到 TPU 上。在 TPU 上运行的应用部分通常用 TensorFlow 编写,并编译成可以在 GPU 或 TPU 上运行的 API。

CPU、GPU、TPU 平台

多数体系架构研究的论文基于运行小型、易于移植的基准测试模拟,这些基准测试可以预测潜在的性能(如果实现的话)。本文与上述论文不同,是对 2015 年以来数据中心运行真实、大型生产工作负载的机器进行回顾性评估,其中一些机器的日常用户超过 10 亿。表 1 中列出的六种应用代表了 2016 年 TPU 数据中心 95% 的使用。

由于测量的是生产环境的负载,要比较的基准平台必须可以在 Google 数据中心部署,因为生产环境的计算负载也就只能在这里运算。谷歌数据中心的很多服务器和谷歌规模对应用程序可靠性的要求意味着机器必须至少检查内存错误。由于英伟达 Maxwell GPU 和最近的 Pascal P40 GPU 不检查内部存储中的错误,以谷歌的规模部署这些处理器、同时还满足谷歌应用程序的严格可靠性要求是做不到的。

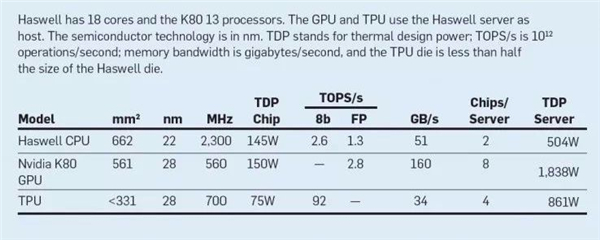

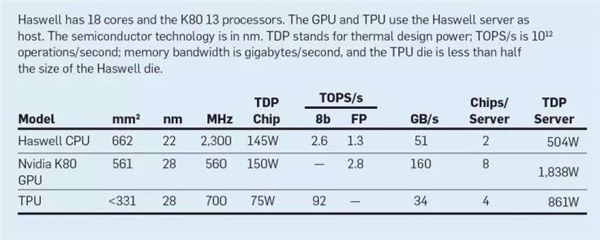

表 2 显示了部署在谷歌数据中心的服务器,可以将其与 TPU 进行比较。传统的 CPU 服务器以英特尔的 18 核双插槽 Haswell 处理器为代表,该平台也是 GPU 或 TPU 的主机服务器。谷歌工程师在服务器中使用了四个 TPU 芯片。

表 2. 基准测试的服务使用Haswell CPU、K80 GPU及TPU

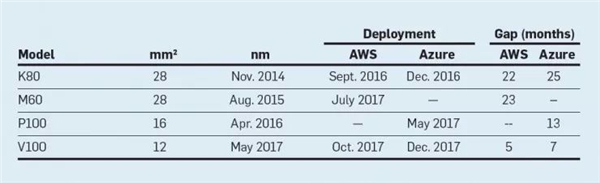

很多计算机架构师没有考虑到从产品发布到芯片、主板、软件可以服务于数据中心的用户之间的时间差。表3指出,2014 年至 2017 年间,商业云公司的 GPU 时间差为 5 至 25 个月。因此,当时适合与 2015 年投入使用的 TPU 的做对比的 GPU 显然是英伟达 K80,后者处于相同的半导体工艺中,并在 TPU 部署前六个月发布。

表 3.2015年到2017年,英伟达GPU从发布到云端部署的时间差距,这4代GPU分别为Kepler、Maxwell、Pascal和Volta架构

每个 K80 卡包含两块硅片,并提供内部存储器和 DRAM 的错误检测和纠错功能。这种服务器中最多可安装 8 个 K80 硅片,这也是我们基准测试的配置。CPU 和 GPU 都使用大型芯片:大约 600 mm2的芯片面积,大约是英特尔 Core i7 的三倍。

性能:Roofline、响应时间、吞吐量

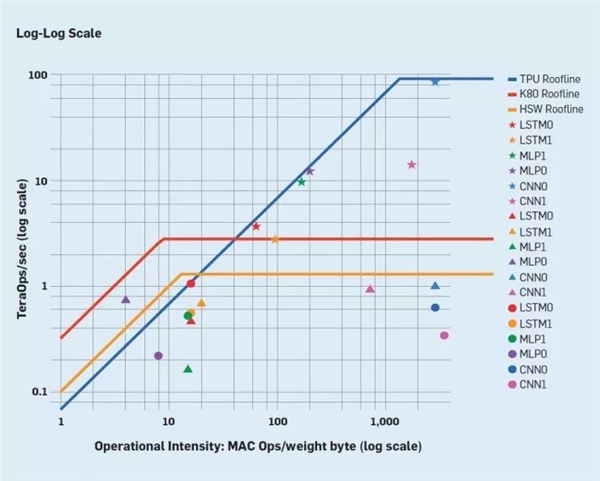

为了说明这六种应用在三类处理器上的性能,我们使用了高性能计算机群(HPC)的 Roofline 性能模型。这一简单的视觉模型虽然不完美,但揭示了性能瓶颈出现的原因。该模型背后的假设是应用需求的计算无法完全装入片上缓存,因此它们要么计算受限,要么内存带宽受限。对于 HPC,y 轴表示每秒浮点运算性能(单位是 FLOPS),因此峰值计算率形成了 roofline 图的“平缓”区。x 轴表示运算密度(operational intensity),单位是 FLOPS/byte。内存带宽表示每秒多少比特,形成了 roofline 的“倾斜”部分,因为 (FLOPS/sec)/ (FLOPS/Byte) = Bytes/sec。没有充足的运算密度时,程序受限于内存带宽,性能只能在 roofline 的“倾斜”部分之下。

一个应用的每秒实际计算量与其天花板计算量之间的距离代表了保持运算密度不变时性能提升的潜力;提升运算密度的优化(如缓存分块)可能带来更大的性能提升。

为了在 TPU 上使用 Roofline 模型,当DNN应用被量化时,我们首先将浮点运算替换成整数运算。由于 DNN 应用的权重通常无法装入片上内存,因此第二个改变就是将运算密度重新定义为每读取 1 字节的权重值时的整数乘积累加运算操作数目,如表1所示。

图 3 展示了单个 TPU、CPU 和 GPU 硅片以 Roofline 模型评估的性能指标,图中是指数坐标。TPU 的 Roofline 模型“倾斜”部分较长,从计算密度角度考虑,这意味着性能更多地受限于内存带宽,而不是计算能力峰值。六个应用中有五个都接近天花板,MLP 和 LSTM 受限于内存,CNN 受限于计算。

图 3:TPU、CPU和GPU在 Roofline 模型上的性能表现。五角星表示TPU,三角形表示英伟达Tesla K80 GPU,圆表示英特尔酷睿处理器(Haswell);所有TPU五角星都与其他两种芯片的 Roofline 模型持平或在后者之上

如图 3 所示,在 Haswell 以及 K80 上,这六个 DNN 应用距离 Roofline 天花板的距离都大于 TPU 上的距离。响应时间是原因所在。这些应用中的很多个是面向终端用户服务的一部分。研究表明,即使响应时间的些微增加都会导致用户使用该服务的频率降低。训练可能没有苛刻的响应时间 deadline,但推理通常有,或者说相比于选择更大吞吐量,推理任务更偏好低延迟。

例如,按照应用开发者的要求,MLP0 应用要求在 99% 的时间内响应时间不大于 7ms。(每秒完成推理的数目要求和 7ms 的延迟要求中包括服务器主机时间和加速器时间)即便对响应时间的限制放宽一些,Haswell 和 K80 运行时也分别只能达到 MLP0 应用最高吞吐量的 42% 和 37%。这些限制也会影响到TPU,它会以 80% 的吞吐量来运行,更加接近 TPU 的 MLP0 最大吞吐量。与 CPU 和 GPU 相比,单线程 TPU 没有复杂的微架构特征,也就不需要为平均状况而消耗晶体管和功率来提高性能,它直接适用于 99% 的状况,即 TPU 没有缓存、分支预测、乱序执行、多处理、推测预读、地址合并、多线程、上下文切等等。极简是领域专用处理器的优势。

表 4 显示了每个芯片的相对推理性能底线,包括两个加速器 vs. CPU 的主机服务器开销,展示了这六个 DNN 应用相对性能的加权平均值,表明 K80 芯片速度是 Haswell 的 1.9 倍,TPU 芯片速度是 Haswell 的 29.2 倍,TPU 芯片速度也就是 GPU 的 15.3 倍。

表 4:在 DNN 工作负载下 K80 GPU 芯片和 TPU 芯片与 CPU 的性能比。加权平均值使用了表 1 中六个 app 的实际混合

性价比、全周期成本(TCO)、性能/功耗

大批量购买计算机时会更多地考虑性价比而非性能。数据中心最好的成本指标是全周期成本(TCO)。一个组织(如谷歌)购买数千张芯片时所支付的实际价格取决于与相关企业的谈判沟通。由于涉及商业机密,我们无法公开此类价格信息或数据。但是,功率与 TCO 相关,我们可以公开每台服务器的功耗数,因此这里我们使用性能/功耗比代替性能/TCO 比。这部分我们对比了整个服务器而不是单个芯片。

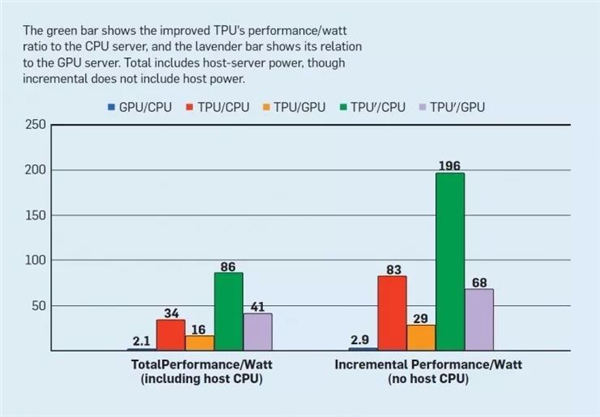

图 4 显示了 K80 GPU 和 TPU 相对于 Haswell CPU 的平均性能/功耗比。我们给出了两种不同的性能/功耗比计算。我们展示了两种不同的性能/功耗计算方法。第一种“total”包括计算 GPU 和 TPU 的性能/功耗时主机 CPU 服务器所消耗的功率;第二种“incremental”从 GPU 和 TPU 中减去了主机 CPU 服务器所消耗的功率。

图 4:GPU 服务器与 CPU 服务器的性能/功耗对比(蓝色条)、TPU 服务器与 CPU 服务器的功耗对比(红色条)、TPU 服务器与 GPU 服务器的功耗对比(橙色条)。TPU' 是使用 K80 的 GDDR5 内存将 TPU 进行改进后的芯片

对于总性能/瓦特,K80 服务器是 Haswell 的2.1倍。 对于增量性能/瓦特,当忽略 Haswell 服务器电源时,K80 服务器是 Haswell 的 2.9 倍。TPU 服务器的总性能/瓦特比 Haswell 要高出34倍,TPU 服务器的性能/功率也就是 K80 服务器的 16 倍。 对于 TPU 来说,相比 CPU 的相对增量性能/瓦特以谷歌设计 ASIC 的水平已经做到了 83 倍,同时也就是 GPU 的性能/瓦特的29倍。

对替代性 TPU 设计的评估

和 FPU 类似,TPU 协同处理器比较容易评估,因此我们为六个应用创建了一个性能模型。模型模拟的结果和硬件实际性能的平均差距小于 10%。

我们使用性能模型评估了另一款假想的 TPU 芯片,记为 TPU'(使用同样的半导体技术再多花 15 个月我们就能设计出这款芯片)。更激进的逻辑合成和模块设计可以把时钟频率再提高 50%;为 GDDR5 内存设计接口电路(就像 K80 那样)可以将权重读取的内存带宽提高四倍,将 roofline 从斜到平的拐点从 1350 降到 250。

单独将时钟频率提高到 1,050 MHz 而不改善内存的话,性能提升非常有限。如果我们把时钟频率保持在 700MHz,但改用 GDDR5 作为内存,则加权平均值飞跃至 3.9倍。同时做这两种措施其实并不会改变性能,因此假设的 TPU' 只具备更快的内存就够了。

将 DDR3 权重内存替换成与 K80 相同 GDDR5 内存需要将内存通道的数量翻一倍,即 4 个通道。这一改进会需要将芯片面积扩大约 10%。GDDR5 还需要将 TPU 系统的功率预算从 861W 提高到 900W 左右,因为每台服务器都有四个 TPU。

从图4可看出,TPU'的总体每硅片性能/功耗是 Haswell 的 86 倍,K80 的 41 倍。其 incremental 指标是 Haswell 的 196 倍,K80 的 68 倍。

讨论

这部分按照 Hennessy 和 Patterson 的谬误-陷阱-反驳格式来展开:

谬误:数据中心的 DNN 推断应用将吞吐量和响应时间处于同等重要的地位。

我们惊讶于谷歌 TPU 开发者对响应时间有这么高的要求,2014 年有人透露说的是:对于 TPU 来说,批量大小应该足够大,以到达 TPU 的计算性能峰值,对延迟的要求不用那么苛刻。一个起到推动作用的应用是离线图像处理,谷歌开发者的直觉是,如果交互式服务也需要 TPU,则大部分服务需要累积足够大的批量然后才交给 TPU 计算。即使 2014 年谷歌关注响应时间(LSTM1)的应用开发者称,2014 年的限制是 10ms,而真正向 TPU 移植时 10ms 将被减少至 7ms。很多此类服务对 TPU 的意料之外的要求,以及它们对快速响应时间的影响和偏好,改变了这个等式。应用编写者通常会选择降低延迟,而不是累积更大的批量。幸运的是,TPU 具备一个简单、可重复的执行模型,来满足交互式服务的低响应时间以及高峰值吞吐量要求,即便是计算相对较小的批量时也比当前 CPU 和 GPU 具备更好的性能。

谬误:K80 GPU 架构很适合进行 DNN 推理。

我们发现 TPU 在性能、能耗和成本方面优于 K80 GPU 有五个方面的原因。1、TPU 只有一个处理器,而 K80 有 13 个,单线程当然更容易满足严格的延迟目标。2、TPU 具备一个非常大的二维乘法单元,GPU 有 13 个小的一维乘法单元。DNN 的矩阵相乘密度适合二维阵列中的算术逻辑运算单元。3、二维阵列还能通过避免访问寄存器来促成脉动式的芯片实现,节约能源。4、TPU 的量化应用使用 8 位整型,而不是 GPU 的 32 位浮点; K80 并不支持 8 位整型。使用更小的数据,改善的不仅是计算能耗,还能四倍化权重 FIFO 的有效容量和权重内存的有效带宽。(尽管推理时使用的是 8 位整型,但训练这些应用时会保证和使用浮点一样的准确率)5、TPU 忽略 GPU 需要而 DNN 不需要的特征,从而缩小 TPU 芯片、节约能耗、为其他改进留下空间。TPU 芯片的大小几乎是 K80 的一半,通常运行所需能量是后者的三分之一,而它的内存却是后者的 3.5 倍。这五个因素导致 TPU 在能耗和性能方面优于 K80 GPU 30 倍。

陷阱:在设计领域专用架构时不顾架构历史。

不适用通用计算的想法可能适合领域专用架构。对于 TPU 而言,三个重要的架构特征可以追溯到 1980 年代早期:脉动阵列(systolic array)、解耦访问/执行(decoupled access/execute)和复杂的指令集。第一个特征减少了大型矩阵相乘单元的面积和能耗;第二个特征在矩阵相乘单元运算期间并行获取权重;第三个特征更好地利用 PCIe bus 的有限带宽来发送指令。因此,对计算机架构历史比较了解的领域专用架构设计师具备竞争优势。

谬误:如果谷歌对 CPU 的使用更加高效,它得到的结果将可以媲美 TPU。

由于有效使用 CPU 的高级向量扩展(AVX2)对整型计算做高效的支持需要大量工作,最初在 CPU 上只有一个 DNN 有 8 位整型的性能测试结果,它的性能提升大约是 3.5 倍。所有的 CPU 性能评估都基于浮点的计算性能来展示会更明确(也不会占太多图表空间),也就没有给这个整型计算结果绘制单独的 Roofline 图。如果所有 DNN 都能够得到类似的加速,TPU 带来的性能/功耗比提升将分别从 41 倍和 83 倍降为 12 倍和 24 倍。

谬误:如果谷歌使用合适的新版本,GPU 结果将与 TPU 差不多。

表 3 报告了发布 GPU 和客户何时可以在云中使用 GPU 的区别。与较新的 GPU 进行公平比较将包括新的 TPU,而对于额外增加的 10W 功耗,我们只需使用 K80 的 GDDR5 内存就可以将 28 纳米、0.7GHz、40W TPU 的性能提高三倍。把 TPU 移动到 16 纳米工艺将进一步提高其性能/功耗。16 纳米英伟达 Pascal P40 GPU 的峰值性能是第一代TPU 的一半,但它 250 瓦的能耗却是原来的很多倍。如前所述,缺乏错误检测意味着 Google 无法再去数据中心部署 P40,因此无法在它们身上运行生产工作负载来确定其实际相对性能。

相关研究

两篇介绍 DNN ASIC 的研究文章至少可以追溯到 20 世纪 90 年代初。如 2016 年的 ACM 通讯中所述,DianNao 家族有四种 DNN 架构,通过对 DNN 应用程序中的内存访问模式提供有效的架构支持,可以最大限度地减少片上和外部 DRAM 的内存访问。最初的 DianNao 使用 64 个 16 位整数乘法累加单元的阵列。

谷歌 TPU 3.0 于今年 5 月推出,其功能是 TPU 2.0 的八倍,性能高达 100petaflops,芯片使用液体冷却为 DNN 设计特定领域架构仍然是计算机架构师的热门话题,其中一个焦点是稀疏矩阵的计算架构,这是在 2015 年 TPU 首次部署之后提出的。

Efficient Inference Engine(高效推理机)中有一步单独的初始扫描,它会过滤去掉非常小的值,将权重数量减少到 1/10 左右,然后使用哈夫曼编码进一步缩小数据以提高推理的性能。Cnvlutin 略去了激活输入为零时的乘法运算,这种计算出现的几率可以达到 44%,部分原因是非线性变换函数 ReLU 会把输入的负值转换为零;这种略去计算的做法使平均性能提高了 1.4 倍。

Eyeriss 是一种新颖的低功耗数据流架构,通过游程编码利用数据中的零来减少内存占用,并通过避免输入为零时的计算来节省能耗。Minerva 是一种跨算法、结构和电路学科的协同设计系统,通过量化数据以及对较小的激活函数剪枝的方式把功耗降低到原来的 1/8。这种系统在 2017 年展出的成果是 SCNN——一种稀疏和压缩卷积神经网络的加速器。权重和激活函数都被压缩在 DRAM 和内部缓冲器中,从而减少了数据传输所需的时间和能量,并允许芯片存储更大的模型。

2016 年以来的另一个趋势,是用于训练的特定领域架构。例如,ScaleDeep 就是为 DNN 训练和推理设计的高性能服务器的一次尝试,它包含数千个处理器。其中的每块芯片都以 3:1 的比例包含计算专用模块和存储专用模块,性能优于 GPU 6-28 倍。它支持 16 位或 32 位浮点计算。芯片通过与 DNN 通信模式匹配的高性能互连拓扑连接。和 SCNN 一样,这种拓扑只在 CNN 上评估。2016 年,CNN 仅占谷歌数据中心 TPU 工作量的 5%。计算机架构师期待对其它类型的 DNN 和硬件实现进行 ScaleDeep 评估。

DNN 似乎是 FPGA 作为数据中心计算平台的一个良好用例。实际部署的一个例子是 Catapult。尽管 Catapult 是在 2014 年公开发布的,但它与 TPU 是同一个时代的,因为 2015 年在微软数据中心部署了 28 纳米 Stratix V FPGA,与谷歌部署 TPU 差不多在同一时间。Catapult 运行 CNN 比普通服务器快 2.3 倍。也许 Catapult 和 TPU 最显着的区别在于,为了获得最佳性能,用户必须使用低级硬件设计语言 Verilog 为 FPGA 编写长程序,而不是使用高级 TensorFlow 框架编写短程序;也就是说,“可再编程性”(re-programmability)来自于 TPU 的软件,而不是最快 FPGA 的固件。

总结

尽管 TPU 在 I/O 总线上,并且内存带宽相对有限限制了它发挥全部效能(六个 DNN 应用程序中有四个受限于内存),但一个很大的数即便拆到很细,拆到每个周期 65536 次乘法累加计算,仍然是一个相对较大的数字,如 roofline 性能模型所示。这个结果表明,Amdahl 定律的其实有一个非常有价值的推论——大量廉价资源的低效利用仍然可以提供颇具性价比的高性能。

我们了解到,推理应用具有严格的响应时间限制,因为它们通常是面向用户的应用;因此,为 DNN 设计计算芯片的设计师们需要保证满足 99% 情况下的时间限制要求。

TPU 芯片利用其在 MAC 和片上内存的优势运行使用特定领域 TensorFlow 框架编写的短程序,该 TensorFlow 框架比 K80 GPU 芯片快 15 倍,因此能获得 29 倍的性能/功耗优势,这与性能/总拥有成本相关。与 Haswell CPU 芯片相比,对应的比率分别为 29 和 83 倍。

有五个架构因素可以解释这种性能差距:

处理器。TPU只有一个处理器,而K80有13个,CPU有18个;单线程使系统更容易保持在固定的延迟限制内。

大型二维乘法单元。TPU有一个非常大的二维乘法单元,而CPU和GPU分别只有18个和13个较小的一维乘法单元;二维硬件在矩阵乘法中有很好的性能。

脉动阵列。二维组织支持脉动阵列,减少寄存器访问和能量消耗。

8位整型。TPU的应用使用 8 位整型而不是 32 位浮点运算来提高计算和内存效率。

弃掉的特征。TPU放弃了 CPU 和 GPU 需要但是 DNN 用不到的功能,这使得 TPU 更便宜,同时可以节约资源,并允许晶体管被重新用于特定领域的板载内存。

虽然未来的 CPU 和 GPU 在运行推理时速度更快,但是使用 circa-2015 型 GPU 内存重新设计的 TPU 将比原来快三倍,并使其性能/功耗优势分别为 K80 和 Haswell 的 70 倍和 200 倍。

至少在过去十年中,计算机架构研究人员发布的创新成果都是来自模拟计算的,这些成果使用了有限的基准,对于通用处理器的改进也只有 10% 或更少,而我们现在报告的性能提升是原来的十倍不止,这是应用于真实生产应用的真实硬件中部署的特定领域架构的收益。

商业产品之间的数量级差异在计算机架构中很少见,而这甚至可能导致 TPU 成为该领域未来工作的典范。我们预计,其他人也会跟进这个方向,并将门槛提得更高。